PCB设计

1、如何选择PCB板材?

选择PCB板材必须在满足设计需求和可量产性及成本中间取得平衡点。设计需求包含电气和机构这两部分。通常在设计非常高速的PCB板子(大于GHz的频率)时这材质问题会比较重要。例如,现在常用的FR-4材质,在几个GHz的频率时的介质损(dielectric loss)会对信号衰减有很大的影响,可能就不合用。就电气而言,要注意介电常数(dielectric constant)和介质损在所设计的频率是否合用。

2、如何避免高频干扰?

避免高频干扰的基本思路是尽量降低高频信号电磁场的干扰,也就是所谓的串扰(Crosstalk)。可用拉大高速信号和模拟信号之间的距离,或加ground guard/shunt traces在模拟信号旁边。还要注意数字地对模拟地的噪声干扰。

3、在高速设计中,如何解决信号的完整性问题?

信号完整性基本上是阻抗匹配的问题。而影响阻抗匹配的因素有信号源的架构和输出阻抗(output impedance),走线的特性阻抗,负载端的特性,走线的拓朴(topology)架构等。解决的方式是靠端接(termination)与调整走线的拓朴。

4、差分布线方式是如何实现的?

差分对的布线有两点要注意,一是两条线的长度要尽量一样长,另一是两线的间距(此间距由差分阻抗决定)要一直保持不变,也就是要保持平行。平行的方式有两种,一为两条线走在同一走线层(side-by-side),一为两条线走在上下相邻两层(over-under)。一般以前者side-by-side实现的方式较多。

5、对于只有一个输出端的时钟信号线,如何实现差分布线?

要用差分布线一定是信号源和接收端也都是差分信号才有意义。所以对只有一个输出端的时钟信号是无法使用差分布线的。

6、接收端差分线对之间可否加一匹配电阻?

接收端差分线对间的匹配电阻通常会加, 其值应等于差分阻抗的值。这样信号品质会好些。

7、为何差分对的布线要靠近且平行?

对差分对的布线方式应该要适当的靠近且平行。所谓适当的靠近是因为这间距会影响到差分阻抗(differential impedance)的值, 此值是设计差分对的重要参数。需要平行也是因为要保持差分阻抗的一致性。若两线忽远忽近, 差分阻抗就会不一致, 就会影响信号完整性(signal integrity)及时间延迟(timing delay)。

8、如何处理实际布线中的一些理论冲突的问题

A. 基本上, 将模/数地分割隔离是对的。

要注意的是信号走线尽量不要跨过有分割的地方(moat), 还有不要让电源和信号的回流电流路径(returning current path)变太大。

B. 晶振是模拟的正反馈振荡电路, 要有稳定的振荡信号, 必须满足loop gain与phase的规范, 而这模拟信号的振荡规范很容易受到干扰, 即使加ground guard traces可能也无法完全隔离干扰。

而且离的太远, 地平面上的噪声也会影响正反馈振荡电路。 所以, 一定要将晶振和芯片的距离进可能靠近。

C. 确实高速布线与EMI的要求有很多冲突。 但基本原则是因EMI所加的电阻电容或ferrite bead, 不能造成信号的一些电气特性不符合规范。

所以, 最好先用安排走线和PCB叠层的技巧来解决或减少EMI的问题, 如高速信号走内层。 最后才用电阻电容或ferrite bead的方式, 以降低对信号的伤害。

选择PCB板材必须在满足设计需求和可量产性及成本中间取得平衡点。设计需求包含电气和机构这两部分。通常在设计非常高速的PCB板子(大于GHz的频率)时这材质问题会比较重要。例如,现在常用的FR-4材质,在几个GHz的频率时的介质损(dielectric loss)会对信号衰减有很大的影响,可能就不合用。就电气而言,要注意介电常数(dielectric constant)和介质损在所设计的频率是否合用。

2、如何避免高频干扰?

避免高频干扰的基本思路是尽量降低高频信号电磁场的干扰,也就是所谓的串扰(Crosstalk)。可用拉大高速信号和模拟信号之间的距离,或加ground guard/shunt traces在模拟信号旁边。还要注意数字地对模拟地的噪声干扰。

3、在高速设计中,如何解决信号的完整性问题?

信号完整性基本上是阻抗匹配的问题。而影响阻抗匹配的因素有信号源的架构和输出阻抗(output impedance),走线的特性阻抗,负载端的特性,走线的拓朴(topology)架构等。解决的方式是靠端接(termination)与调整走线的拓朴。

4、差分布线方式是如何实现的?

差分对的布线有两点要注意,一是两条线的长度要尽量一样长,另一是两线的间距(此间距由差分阻抗决定)要一直保持不变,也就是要保持平行。平行的方式有两种,一为两条线走在同一走线层(side-by-side),一为两条线走在上下相邻两层(over-under)。一般以前者side-by-side实现的方式较多。

5、对于只有一个输出端的时钟信号线,如何实现差分布线?

要用差分布线一定是信号源和接收端也都是差分信号才有意义。所以对只有一个输出端的时钟信号是无法使用差分布线的。

6、接收端差分线对之间可否加一匹配电阻?

接收端差分线对间的匹配电阻通常会加, 其值应等于差分阻抗的值。这样信号品质会好些。

7、为何差分对的布线要靠近且平行?

对差分对的布线方式应该要适当的靠近且平行。所谓适当的靠近是因为这间距会影响到差分阻抗(differential impedance)的值, 此值是设计差分对的重要参数。需要平行也是因为要保持差分阻抗的一致性。若两线忽远忽近, 差分阻抗就会不一致, 就会影响信号完整性(signal integrity)及时间延迟(timing delay)。

8、如何处理实际布线中的一些理论冲突的问题

A. 基本上, 将模/数地分割隔离是对的。

要注意的是信号走线尽量不要跨过有分割的地方(moat), 还有不要让电源和信号的回流电流路径(returning current path)变太大。

B. 晶振是模拟的正反馈振荡电路, 要有稳定的振荡信号, 必须满足loop gain与phase的规范, 而这模拟信号的振荡规范很容易受到干扰, 即使加ground guard traces可能也无法完全隔离干扰。

而且离的太远, 地平面上的噪声也会影响正反馈振荡电路。 所以, 一定要将晶振和芯片的距离进可能靠近。

C. 确实高速布线与EMI的要求有很多冲突。 但基本原则是因EMI所加的电阻电容或ferrite bead, 不能造成信号的一些电气特性不符合规范。

所以, 最好先用安排走线和PCB叠层的技巧来解决或减少EMI的问题, 如高速信号走内层。 最后才用电阻电容或ferrite bead的方式, 以降低对信号的伤害。

下面是我对电源回流的理解,跟大家分享一下^_^(其中介绍的一些处理方法在国内外很多高速PCB电路里都有应用的)

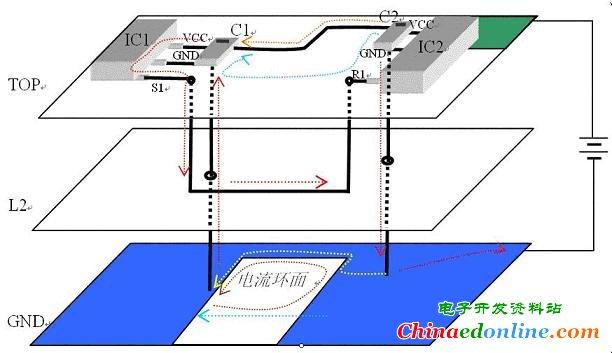

这里简单构造了一个“场景”,结合下图介绍一下地回流和电源回流以及一些跨分割问题。为方便作图,把层间距放大。

IC1为信号输出端,IC2为信号输入端(为简化PCB模型,假定接收端内含下接电阻)第三层为地层。IC1和IC2的地均来自于第三层地层面。顶层右上角为一块电源平面,接到电源正极。C1和C2分别为IC1、IC2的退耦电容。图上所示的芯片的电源和地脚均为发、收信号端的供电电源和地。

在低频时,如果S1端输出高电平,整个电流回路是电源经导线接到VCC电源平面,然后经橙色路径进入IC1,然后从S1端出来,沿第二层的导线经R1端进入IC2,然后进入GND层,经红色路径回到电源负极。

但在高频时,PCB所呈现的分布特性会对信号产生很大影响。我们常说的地回流就是高频信号中经常要遇到的一个问题。当S1到R1的信号线中有增大的电流时,外部的磁场变化很快,会使附近的导体感应出一个反向的电流。如果第三层的地平面是完整的地平面的话,那么会在地平面上会有一个蓝色虚线标示的电流;如果TOP层有一个完整的电源平面的话,也会在顶层有一个沿蓝色虚线的回流。此时信号回路有最小的电流回路,向外辐射的能量最小,耦合外部信号的能力也最小。(高频时的趋肤效应也是向外辐射能量最小,原理是一样的。)

由于高频信号电平和电流变化都很快,但是变化周期短,需要的能量并不是很大,所以芯片是和离芯片最近的退耦电容取电的。当C1足够大,而且反应又足够快(有很低的ESR值,通常用瓷片电容。瓷片电容的ESR远低于钽电容。),位于顶层的橙色路径和位于GND层的红色路径可以看成是不存在的(存在一个和整板供电对应的电流,但不是与图示信号对应的电流)。

因此,按图中构造的环境,电流的整个通路是:由C1的正极->IC1的VCC->S1->L2信号线->R1->IC2的GND->过孔->GND层的黄色路径->过孔->电容负极。可以看到,电流的垂直方向有一个棕色的等效电流,中间会感应出磁场,同时,这个环面也能很容易的耦合到外来的干扰。如果和图中信号为一条时钟信号,并行有一组8bit的数据线,由同一芯片的同一电源供电,电流回流途径是相同的。如果数据线电平同时同向翻转的话,会使时钟上感应一个很大的反向电流,如果时钟线没有良好的匹配的话,这个串扰足以对时钟信号产生致命影响。这种串扰的强度不是和干扰源的高低电平的绝对值成正比,而是和干扰源的电流变化速率成正比,对于一个纯阻性的负载来说,串扰电流正比于dI/dt=dV/(T10%-90%*R)。式中的dI/dt (电流变化速率)、dV(干扰源的摆幅)和R(干扰源负载)都是指干扰源的参数(如果是容性负载的话,dI/dt是与T10%-90%的平方成反比的。)。从式中可以看出,低速的信号未必比高速信号的串扰小。也就是我们说的:1kHZ的信号未必是低速信号,要综合考虑沿的情况。对于沿很陡的信号,是包含很多谐波成分的,在各倍频点都有很大的振幅。因此,在选器件的时候也要注意一下,不要一味选开关速度快的芯片,不仅成本高,还会增加串扰以及EMC问题。

任何相邻的电源层或其它的平面,只要在信号两端有合适的电容提供一个到GND的低电抗通路,那么这个平面就可以作为这个信号的回流平面。在平常的应用中,收发对应的芯片IO电源往往是一致的,而且各自的电源与地之间一般都有0.01-0.1uF的退耦电容,而这些电容也恰恰在信号的两端,所以该电源平面的回流效果是仅次于地平面的。而借用其他的电源平面做回流的话,往往不会在信号两端有到地的低电抗通路。这样,在相邻平面感应出的电流就会寻找最近的电容回到地。如果这个“最近的电容”离始端或终端很远的话,这个回流也要经过“长途跋涉”才能形成一个完整的回流通路,而这个通路也是相邻信号的回流通路,这个相同的回流通路和共地干扰的效果是一样的,等效为信号之间的串扰。

对于一些无法避免的跨电源分割的情况,可以在跨分割的地方跨接电容或RC串联构成的高通滤波器(如10欧电阻串680p电容,具体的值要依自己的信号类型而定,即要提供高频回流通路,又要隔离相互平面间的低频串扰)。这样可能会涉及到在电源平面之间加电容的问题,似乎有点滑稽,但肯定是有效的。如果一些规范上不允许的话,可以在分割处两平面分别引电容到地。

对于借用其它平面做回流的情况,最好能在信号两端适当增加几个小电容到地,提供一个回流通路。但这种做法往往难以实现。因为终端附近的表层空间大多都给匹配电阻和芯片的退耦电容占据了。

时间原因就先写这些…如果有遗漏或错误的地方请大家提醒。共同学习提高^_^。

这里简单构造了一个“场景”,结合下图介绍一下地回流和电源回流以及一些跨分割问题。为方便作图,把层间距放大。

IC1为信号输出端,IC2为信号输入端(为简化PCB模型,假定接收端内含下接电阻)第三层为地层。IC1和IC2的地均来自于第三层地层面。顶层右上角为一块电源平面,接到电源正极。C1和C2分别为IC1、IC2的退耦电容。图上所示的芯片的电源和地脚均为发、收信号端的供电电源和地。

在低频时,如果S1端输出高电平,整个电流回路是电源经导线接到VCC电源平面,然后经橙色路径进入IC1,然后从S1端出来,沿第二层的导线经R1端进入IC2,然后进入GND层,经红色路径回到电源负极。

但在高频时,PCB所呈现的分布特性会对信号产生很大影响。我们常说的地回流就是高频信号中经常要遇到的一个问题。当S1到R1的信号线中有增大的电流时,外部的磁场变化很快,会使附近的导体感应出一个反向的电流。如果第三层的地平面是完整的地平面的话,那么会在地平面上会有一个蓝色虚线标示的电流;如果TOP层有一个完整的电源平面的话,也会在顶层有一个沿蓝色虚线的回流。此时信号回路有最小的电流回路,向外辐射的能量最小,耦合外部信号的能力也最小。(高频时的趋肤效应也是向外辐射能量最小,原理是一样的。)

由于高频信号电平和电流变化都很快,但是变化周期短,需要的能量并不是很大,所以芯片是和离芯片最近的退耦电容取电的。当C1足够大,而且反应又足够快(有很低的ESR值,通常用瓷片电容。瓷片电容的ESR远低于钽电容。),位于顶层的橙色路径和位于GND层的红色路径可以看成是不存在的(存在一个和整板供电对应的电流,但不是与图示信号对应的电流)。

因此,按图中构造的环境,电流的整个通路是:由C1的正极->IC1的VCC->S1->L2信号线->R1->IC2的GND->过孔->GND层的黄色路径->过孔->电容负极。可以看到,电流的垂直方向有一个棕色的等效电流,中间会感应出磁场,同时,这个环面也能很容易的耦合到外来的干扰。如果和图中信号为一条时钟信号,并行有一组8bit的数据线,由同一芯片的同一电源供电,电流回流途径是相同的。如果数据线电平同时同向翻转的话,会使时钟上感应一个很大的反向电流,如果时钟线没有良好的匹配的话,这个串扰足以对时钟信号产生致命影响。这种串扰的强度不是和干扰源的高低电平的绝对值成正比,而是和干扰源的电流变化速率成正比,对于一个纯阻性的负载来说,串扰电流正比于dI/dt=dV/(T10%-90%*R)。式中的dI/dt (电流变化速率)、dV(干扰源的摆幅)和R(干扰源负载)都是指干扰源的参数(如果是容性负载的话,dI/dt是与T10%-90%的平方成反比的。)。从式中可以看出,低速的信号未必比高速信号的串扰小。也就是我们说的:1kHZ的信号未必是低速信号,要综合考虑沿的情况。对于沿很陡的信号,是包含很多谐波成分的,在各倍频点都有很大的振幅。因此,在选器件的时候也要注意一下,不要一味选开关速度快的芯片,不仅成本高,还会增加串扰以及EMC问题。

任何相邻的电源层或其它的平面,只要在信号两端有合适的电容提供一个到GND的低电抗通路,那么这个平面就可以作为这个信号的回流平面。在平常的应用中,收发对应的芯片IO电源往往是一致的,而且各自的电源与地之间一般都有0.01-0.1uF的退耦电容,而这些电容也恰恰在信号的两端,所以该电源平面的回流效果是仅次于地平面的。而借用其他的电源平面做回流的话,往往不会在信号两端有到地的低电抗通路。这样,在相邻平面感应出的电流就会寻找最近的电容回到地。如果这个“最近的电容”离始端或终端很远的话,这个回流也要经过“长途跋涉”才能形成一个完整的回流通路,而这个通路也是相邻信号的回流通路,这个相同的回流通路和共地干扰的效果是一样的,等效为信号之间的串扰。

对于一些无法避免的跨电源分割的情况,可以在跨分割的地方跨接电容或RC串联构成的高通滤波器(如10欧电阻串680p电容,具体的值要依自己的信号类型而定,即要提供高频回流通路,又要隔离相互平面间的低频串扰)。这样可能会涉及到在电源平面之间加电容的问题,似乎有点滑稽,但肯定是有效的。如果一些规范上不允许的话,可以在分割处两平面分别引电容到地。

对于借用其它平面做回流的情况,最好能在信号两端适当增加几个小电容到地,提供一个回流通路。但这种做法往往难以实现。因为终端附近的表层空间大多都给匹配电阻和芯片的退耦电容占据了。

时间原因就先写这些…如果有遗漏或错误的地方请大家提醒。共同学习提高^_^。

设计高频电路用电路板有许多注意事项,尤其是GHz等级的高频电路,更需要注意各电子组件pad与印刷pattern的长度对电路特性所造成的影响。最近几年高频电路与数字电路共享相同电路板,构成所谓的混载电路系统似乎有增加的趋势,类似如此的设计经常会造成数字电路动作时,高频电路却发生动作不稳定等现象,其中原因之一是数字电路产生的噪讯,影响高频电路正常动作所致。为了避免上述问题除了设法分割两电路block之外,设计电路板之前充分检讨设计构想,才是根本应有的手法,基本上设计高频电路用电路板必需掌握下列三大原则:

1.高质感。

2.不可取巧。

3.不可仓促抢时间。

设计高频电路板的基本常识

以下是设计高频电路板的基本常识:

(a).印刷pattern的长度会影响电路特性。

尤其是传输速度为GHz高速数字电路的传输线路,通常会使用strip line,同

时藉由调整配线长度补正传输延迟时间,其实这也意味着电子组件的设置位置对电路特性具有绝对性的影响。

(b).Ground作大better。

铜箔面整体设置ground层,而连接via的better ground则是高频电路板与高速数字电路板共同的特征,此外高频电路板最忌讳使用幅宽细窄的印刷pattern描绘ground。

(c).电子组件的ground端子,以最短的长度与电路板的ground连接。

具体方法是在电子组件的ground端子pad附近设置via,使电子组件能以最短的长度与电路板的ground连接。

(d).信号线作短配线设计。

不可任意加大配线长度,尽量缩短配线长度。

(e).减少电路之间的结合。

尤其是filter与amplifier输出入之间作电路分割非常重要,它相当于audio电路的cross talk对策。

高频电路板的设计步骤

高频电路板的设计步骤大致上可整理成如下:

1.根据外筐尺寸的限制,决定电路板的大小。

2.制作印刷电路板外形,与library的data。

3.决定高频电路单元与信号处理单元的封装位置。

基本上高频电路单元与模拟/数字信号处理单元必需分开封装,分割方式有两种分别如下:

(a).将电路板正面与反面的的高频电路单元与数字信号处理单元分开,主要原因是数字电路的噪讯很容易流入高频电路单元,高频电路单元的背面设置数字电路时,必需避免两者的封装在相同角落上。

(b).将电路板对分成高频电路单元与数字信号处理单元各占一半的场合,高频电路单元的控制信号线回绕长度如果过过长时,很容易受到数字电路噪讯的影响

4.电路板设置电子组件。

组件设置作业对设计高频电路板而言具有决定性的影响,尤其是包含ground via与连接via的面积,以及如何确保电子组件之间的space等设计非常的重要,例如电子组件之间的space设计不当的话,将招致无法设置ground via,以及无法连接via等严重后果,也就是说电子组件的配置是否适宜,会使高频电路的性能产生重大变化。

5.设计配线

除了印刷pattern的配线之外,同时还需要调整line的阻抗(impedance),并设置ground via。

6.检查配线

完成电路板data之后必需检查设计规范(rule),尤其是检查print out的配线是否有任何设计上的疏失,如果电路板有正、反面辨识上的需求时,可提出数据数据要求厂商制作。

设计高频电路板的四大要诀

(一).利用印刷pattern取代被动电子组件的功能

照片1是1.5GHz RF增幅器电路板封装后的外观;图1是RF增幅器的电路layout图。该电路的噪讯值为0.6~0.7dB,电路板中央部位附近设有富士通编号为FHC30 FA的HEMT(High Electron Mobility Transistor)电子组件。图1中的MS组件是表示micro strip,由于电容与线圈的功能可利用micro strip实现,因此该电路并未使用被动电子组件。例如照片1之中与HEMT gate垂直延伸的印刷pattern (简称为open stub),就可发挥电容的功能。此外基于增幅器的稳定性必需取得等化,因此input电路整合ГOPT (NF最小点),output电路的阻抗(impedance)则作50Ω的设计整合。由于整合用的device也是用印刷pattern形成,所以实际设计电路板时必需将长度与宽度作严谨的配合。

照片1 高频电路板利用印刷pattern,取代被动电子组件设计实例

图1 照片1的1.5GHz RF增幅器电路图

(二).电子组件沿着信号传输方向排列,降低配线长度

照片2是800MHz RF增幅器电路板封装后的外观;图2是RF增幅器的电路layout图。图2中的低噪讯Transistor电子组件使用NEC的2SC5185,由可知照片2电子组件沿着信号传输方向排列,藉此降低配线长度。

照片2 电子组件沿着信号传输方向排列,降低配线长度的设计实例

图2 照片2的800MHz RF增幅器电路图

(三).Emitter 端子附近设置ground via

如照片2所示高频Transistor组件2SC5185两个Emitter具有四只脚(pin),由照片可看见Emitter端子,pad的附近设有ground via,此种结构一般称为mini mo del type。如果via远离pad,增幅器的特性就会产生巨大变化,严重时甚至无法获得模拟分析预期的等化与阻抗(impedance)特性。从Emitter端子到via的配线,可因micro strip line的结构而产生组件特性,有关它的影响力将在后述章节中会以模拟分析方式深入探讨。总而言之在高频电路板,电子组件ground的处理非常重要。

(四).发热电子组件可利用ground面与金属筐体散热

照片3是800MHz RF送信机后段电路板封装后的外观,由照片可看见FET的source端子附近设有许多与ground层连接的via,这些via除了可以用低阻抗与ground层连接之外,还可将高频电路的送信单元产生的热能排除进而获得散热效果。这种散热方法尤其是对不易将发热组件的热能排除时,可透过电路板的ground铜箔面,将热能导至金属筐体协助散热,如果祇是为了散热,铜箔必需有70~100μm的厚度才能发挥预期的散热效果,因此电路板上的铜箔被视为有效的散热对策之一。

照片3 800MHz RF送信机后段,电路板增加散热用via的设计实例

波长对pattern长度的相关性

*波长与波长的关系

图4是12GHz micro strip edge couple BPF电路板封装后的外观,类似如此超高频的印刷pattern重合部位,不论是长度、宽度与间隔都需作高精度的要求,如果是图2所示的电路板封装方式,基本上不可能获得预期的高频特性。主要原因是两电路板处理的信号频率差异,使得电路板的layout方式也截然不同。假设空气中或是真空中的波长为λ(mm) ,频率为f(GHZ) 时,两者的关系式如下:

表1是利用式(1)试算波长与频率的结果。

频率(GHZ)

真空中的(mm)

1

300

2.4

125

5.6

53.6

12

25

表1 空气中或的波长与频率的关系

照片4 12GHz的micro strip edge couple BPF电路板的设计实例

*印刷电路板上的波长比真空中的波长短

在比诱电率为 的电路板上的信号波长会变短,这种现象称为波长缩短率 ,波长缩短率可用下式表示:

例如G10玻璃环氧树脂(glass epoxy)的 为4.8,如果将该值夜代入式(2)便可求得波长缩短率:

假设800MHz的信号,空间波长为375nm,则玻璃环氧树脂电路板上的波长会缩短为:

375×0.456=171nm

*实际波长可用实效比诱电率计算

实际电路板若是由micro strip line构成的场合,由于电界会外漏至诱电体电路板外面临造成诱电率下降,该诱电率称为实效比诱电率。电路板上的缩短率SPCB 可用下式表示:

表2是1GHz常用的CEM-3与12GHz BS converter常用的PPO,利用MEL的SNAP高频仿真器计算两者实效比诱电率的结果;表3是根据实效比诱电率的计算结果,计算1G Hz与12GHz信号在印刷电路板上的波长。根据仿真分析结果显示传至印刷pattern的高频信号波长,对电路板的材质具有很高的相关性。

诱电体的厚度(t=mm)

实效比诱电率( εr )

特性阻抗 Zo ( Ω )

Line宽度 W(mm)

0.6

3.246

50.07

1.143

1

3.256

50.08

1.92

(a)CEM-3, εr = 4.3,铜箔厚度18μm,频率1GHz

诱电体的厚度(t=mm)

实效比诱电率( εr )

特性阻抗 Zo ( Ω )

Line宽度 W(mm)

0.6

2.591

50.06

1.396

1

2.669

50.06

2.289

(b)PPO,εr = 3.2 ,铜箔厚度18μm,频率10GHz

表2 典型的两种印刷电路板的实效比诱电率

频率

空间波长(λair)

电路板上的波长

(GHz)

SPCB (mm)

SPCB / 4(mm)

1

300

166.5

41.6

12

15.5

3.9

表3 电路板上与空气中的波长差异

1.高质感。

2.不可取巧。

3.不可仓促抢时间。

设计高频电路板的基本常识

以下是设计高频电路板的基本常识:

(a).印刷pattern的长度会影响电路特性。

尤其是传输速度为GHz高速数字电路的传输线路,通常会使用strip line,同

时藉由调整配线长度补正传输延迟时间,其实这也意味着电子组件的设置位置对电路特性具有绝对性的影响。

(b).Ground作大better。

铜箔面整体设置ground层,而连接via的better ground则是高频电路板与高速数字电路板共同的特征,此外高频电路板最忌讳使用幅宽细窄的印刷pattern描绘ground。

(c).电子组件的ground端子,以最短的长度与电路板的ground连接。

具体方法是在电子组件的ground端子pad附近设置via,使电子组件能以最短的长度与电路板的ground连接。

(d).信号线作短配线设计。

不可任意加大配线长度,尽量缩短配线长度。

(e).减少电路之间的结合。

尤其是filter与amplifier输出入之间作电路分割非常重要,它相当于audio电路的cross talk对策。

高频电路板的设计步骤

高频电路板的设计步骤大致上可整理成如下:

1.根据外筐尺寸的限制,决定电路板的大小。

2.制作印刷电路板外形,与library的data。

3.决定高频电路单元与信号处理单元的封装位置。

基本上高频电路单元与模拟/数字信号处理单元必需分开封装,分割方式有两种分别如下:

(a).将电路板正面与反面的的高频电路单元与数字信号处理单元分开,主要原因是数字电路的噪讯很容易流入高频电路单元,高频电路单元的背面设置数字电路时,必需避免两者的封装在相同角落上。

(b).将电路板对分成高频电路单元与数字信号处理单元各占一半的场合,高频电路单元的控制信号线回绕长度如果过过长时,很容易受到数字电路噪讯的影响

4.电路板设置电子组件。

组件设置作业对设计高频电路板而言具有决定性的影响,尤其是包含ground via与连接via的面积,以及如何确保电子组件之间的space等设计非常的重要,例如电子组件之间的space设计不当的话,将招致无法设置ground via,以及无法连接via等严重后果,也就是说电子组件的配置是否适宜,会使高频电路的性能产生重大变化。

5.设计配线

除了印刷pattern的配线之外,同时还需要调整line的阻抗(impedance),并设置ground via。

6.检查配线

完成电路板data之后必需检查设计规范(rule),尤其是检查print out的配线是否有任何设计上的疏失,如果电路板有正、反面辨识上的需求时,可提出数据数据要求厂商制作。

设计高频电路板的四大要诀

(一).利用印刷pattern取代被动电子组件的功能

照片1是1.5GHz RF增幅器电路板封装后的外观;图1是RF增幅器的电路layout图。该电路的噪讯值为0.6~0.7dB,电路板中央部位附近设有富士通编号为FHC30 FA的HEMT(High Electron Mobility Transistor)电子组件。图1中的MS组件是表示micro strip,由于电容与线圈的功能可利用micro strip实现,因此该电路并未使用被动电子组件。例如照片1之中与HEMT gate垂直延伸的印刷pattern (简称为open stub),就可发挥电容的功能。此外基于增幅器的稳定性必需取得等化,因此input电路整合ГOPT (NF最小点),output电路的阻抗(impedance)则作50Ω的设计整合。由于整合用的device也是用印刷pattern形成,所以实际设计电路板时必需将长度与宽度作严谨的配合。

照片1 高频电路板利用印刷pattern,取代被动电子组件设计实例

图1 照片1的1.5GHz RF增幅器电路图

(二).电子组件沿着信号传输方向排列,降低配线长度

照片2是800MHz RF增幅器电路板封装后的外观;图2是RF增幅器的电路layout图。图2中的低噪讯Transistor电子组件使用NEC的2SC5185,由可知照片2电子组件沿着信号传输方向排列,藉此降低配线长度。

照片2 电子组件沿着信号传输方向排列,降低配线长度的设计实例

图2 照片2的800MHz RF增幅器电路图

(三).Emitter 端子附近设置ground via

如照片2所示高频Transistor组件2SC5185两个Emitter具有四只脚(pin),由照片可看见Emitter端子,pad的附近设有ground via,此种结构一般称为mini mo del type。如果via远离pad,增幅器的特性就会产生巨大变化,严重时甚至无法获得模拟分析预期的等化与阻抗(impedance)特性。从Emitter端子到via的配线,可因micro strip line的结构而产生组件特性,有关它的影响力将在后述章节中会以模拟分析方式深入探讨。总而言之在高频电路板,电子组件ground的处理非常重要。

(四).发热电子组件可利用ground面与金属筐体散热

照片3是800MHz RF送信机后段电路板封装后的外观,由照片可看见FET的source端子附近设有许多与ground层连接的via,这些via除了可以用低阻抗与ground层连接之外,还可将高频电路的送信单元产生的热能排除进而获得散热效果。这种散热方法尤其是对不易将发热组件的热能排除时,可透过电路板的ground铜箔面,将热能导至金属筐体协助散热,如果祇是为了散热,铜箔必需有70~100μm的厚度才能发挥预期的散热效果,因此电路板上的铜箔被视为有效的散热对策之一。

照片3 800MHz RF送信机后段,电路板增加散热用via的设计实例

波长对pattern长度的相关性

*波长与波长的关系

图4是12GHz micro strip edge couple BPF电路板封装后的外观,类似如此超高频的印刷pattern重合部位,不论是长度、宽度与间隔都需作高精度的要求,如果是图2所示的电路板封装方式,基本上不可能获得预期的高频特性。主要原因是两电路板处理的信号频率差异,使得电路板的layout方式也截然不同。假设空气中或是真空中的波长为λ(mm) ,频率为f(GHZ) 时,两者的关系式如下:

表1是利用式(1)试算波长与频率的结果。

频率(GHZ)

真空中的(mm)

1

300

2.4

125

5.6

53.6

12

25

表1 空气中或的波长与频率的关系

照片4 12GHz的micro strip edge couple BPF电路板的设计实例

*印刷电路板上的波长比真空中的波长短

在比诱电率为 的电路板上的信号波长会变短,这种现象称为波长缩短率 ,波长缩短率可用下式表示:

例如G10玻璃环氧树脂(glass epoxy)的 为4.8,如果将该值夜代入式(2)便可求得波长缩短率:

假设800MHz的信号,空间波长为375nm,则玻璃环氧树脂电路板上的波长会缩短为:

375×0.456=171nm

*实际波长可用实效比诱电率计算

实际电路板若是由micro strip line构成的场合,由于电界会外漏至诱电体电路板外面临造成诱电率下降,该诱电率称为实效比诱电率。电路板上的缩短率SPCB 可用下式表示:

表2是1GHz常用的CEM-3与12GHz BS converter常用的PPO,利用MEL的SNAP高频仿真器计算两者实效比诱电率的结果;表3是根据实效比诱电率的计算结果,计算1G Hz与12GHz信号在印刷电路板上的波长。根据仿真分析结果显示传至印刷pattern的高频信号波长,对电路板的材质具有很高的相关性。

诱电体的厚度(t=mm)

实效比诱电率( εr )

特性阻抗 Zo ( Ω )

Line宽度 W(mm)

0.6

3.246

50.07

1.143

1

3.256

50.08

1.92

(a)CEM-3, εr = 4.3,铜箔厚度18μm,频率1GHz

诱电体的厚度(t=mm)

实效比诱电率( εr )

特性阻抗 Zo ( Ω )

Line宽度 W(mm)

0.6

2.591

50.06

1.396

1

2.669

50.06

2.289

(b)PPO,εr = 3.2 ,铜箔厚度18μm,频率10GHz

表2 典型的两种印刷电路板的实效比诱电率

频率

空间波长(λair)

电路板上的波长

(GHz)

SPCB (mm)

SPCB / 4(mm)

1

300

166.5

41.6

12

15.5

3.9

表3 电路板上与空气中的波长差异

在电路设计的时候,在一块PCB板上存在多种电源、多种地的情况越来越多,例如48V,12V-12V,5V,-5V,3.3V,2.5V,1.8V1.5V等电源中常见的种类,AGND(模拟地)DGND(数字地)、PGND(保护地)等不同功能所需的地平面纵横交错,一部分IC明确要求本IC要进行单点接地,以及所需的电源、地平面挖空。为了保证这些地、电源都有高的可靠性,将每一种电源、地分配一层,即一个平面,必然导致电路板叠层的增加,电路板制作的成本大幅度升高。前面说过,电路板的制作成本和叠层数成正比。为了兼顾节约成本和保证电路板的可靠性,工程师在PCB设计的时候,会按照电路板的特点、将两种或者几种PCB的电源或地设计在同一个平面上,从而导致了电源、地平面的不完整,即地(电源)层分割。

一、PCB板的跨分割设计

电路上PCB走线穿过地(电源)层分割,信号的完整性会受到很大的影响,以及电路的EMI和EMC特性也发生变化,这就是跨分割问题。这些也往往是电子工程师容易忽略的问题。跨分割问题的产生主要有两个来源:

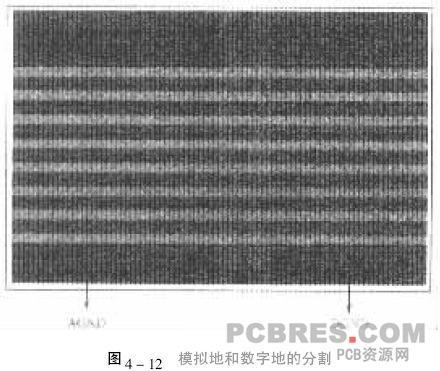

1、电源/地平面的分割

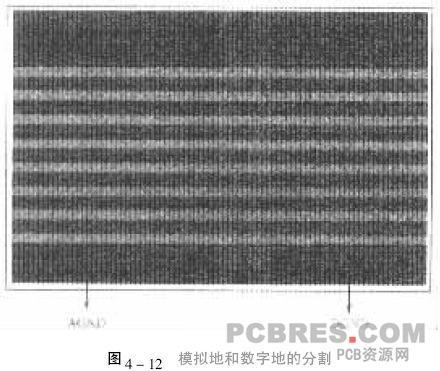

如图4-12所示,在同一层(地层)上有模拟地和数字地的分割。当PCB走线穿过这个分割带时,跨分割问题产生了。

2、密集过孔或密集插装(压接)器件管脚定义不当造成的分割

密集过孔或密集插装(压接)器件在管脚定义时如果分布得不合理,而管脚之间的距离很小,会在地层或者定义层造成了一个狭长的隔离带。如果有走线穿过这个分割,就造成做跨分割现象。

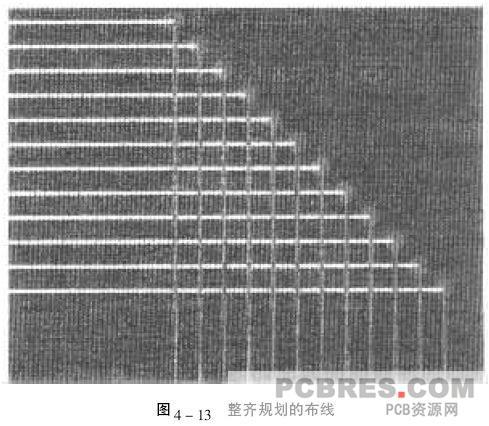

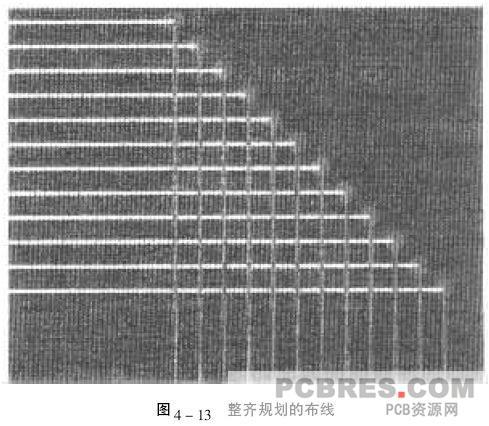

我们先看看如图4-13所示的走线。

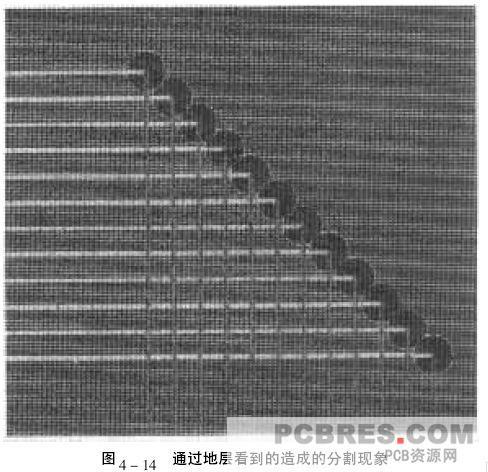

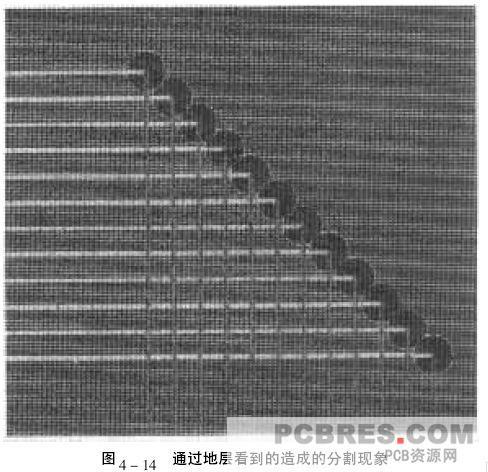

这些布线表面上无可挑剔:整齐,漂亮,也是一般电子或电路工程师所喜欢的布线方式。我们再看一下这些过孔对应区域的电源/地平面(图6-14),就会发现产生了电源、地层分割问题。

在图4-13 中,由于过孔间距过近,在电源/地平面上造成一条长长分割带,如图4-14所示,如果有走线穿过这个分割带时,跨分割问题也产生了。这类问题主要出现在电路中总线布线时容易出现,必须引起广大工程师的注意。

同样地,当通孔(包括焊盘和过孔)穿过地/电源平面时,如果通孔之间的距离靠得过近,上述问题也就同样出现了。这类问题主要出现在密集插装(压接)器件管脚定义不当时容易出现。因此,在定义密集插装(压接)器件管脚信号时,不仅要考虑信号的个数种类,还必须考虑信号总线的排列方式,避免对电源、地平面造成分割带来跨分割问题。

二、PCB板的跨分割走线的危害

跨分割走线的主要危害包括:

(1)导致走线的阻抗不连续;

(2)容易使信号之间发生串扰;

(3)可能引起信号的反射;

(4)增大电流环路面积,加大环路电感,使输出的波形容易振荡;

(5)增加向空间的辐射干扰,同时易受空间磁场的影响;

(6)加大与板上其他电路产生磁场耦合的可能性;

(7)环路电感上的高频压降构成共模辐射源,并通过外接电缆产生共模辐射。

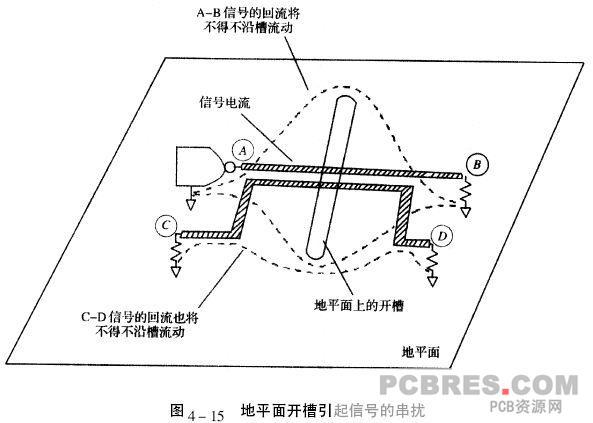

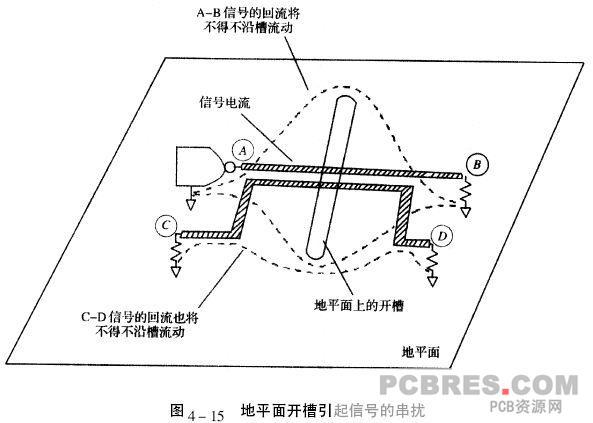

为了形象地描述跨分割走线对电路的危害,我们用图4-15给出了一个地槽引起高频信号产生串扰的示意图。

对于需要严格的阻抗控制、按带状线模型走线的高速信号线而言,还会因为上平面、下平面或上下平面的开槽破坏带状线模型,造成阻抗的不连续,引起严重的信号失真,使信号的可靠度下降。

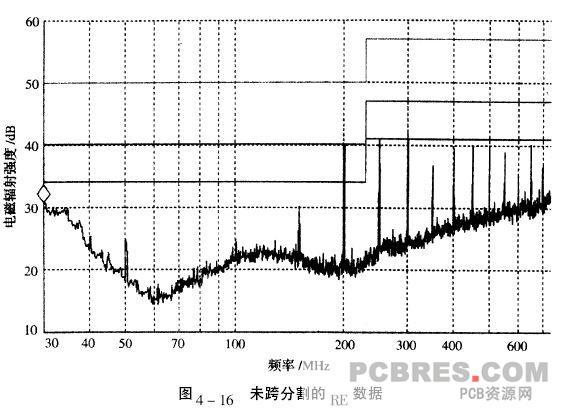

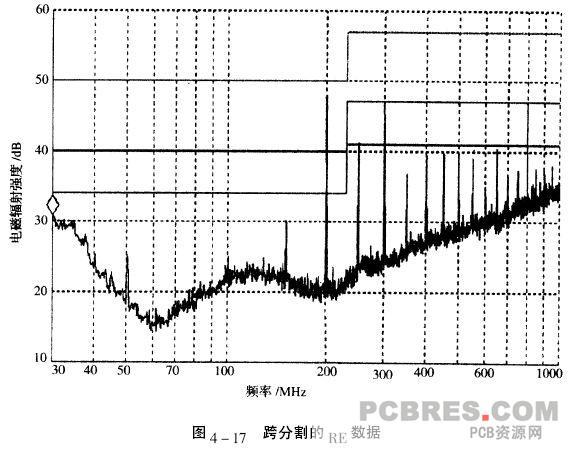

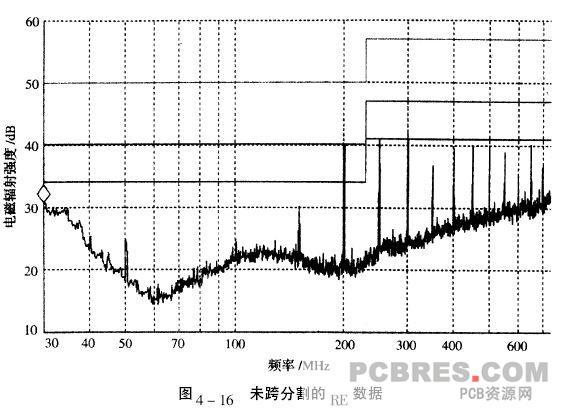

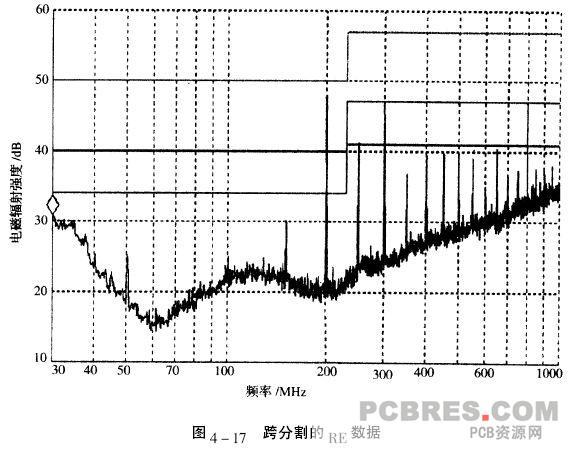

为了形象地描述跨分割走线对电磁干扰的影响,笔者进行“了试验对比。从对比的结果很容易看到跨分割的影响。

在一块PCB板上布了两根走线,两者激励源相同,负载完全一样,均走在同一布线层,长度均为6000MIL,惟一不同的是,一个跨了平面分割,另外一个参考平面完整。通过开关切换,在保证外部条件完全相同的情况下,分别让其中的一个网络上电,在半波暗室测试结果如下:

从图4-16和图4-17可以清楚地看出:信号跨分割区会增加辐射8dB-10dB;具体增加的辐射强度取决于跨分割导致的回流路径回路面积的大小,也与周围的电磁干扰环境有关。如果一条时钟线在对外接口线缆附近跨分割布线,其导致的电磁干扰强度可能超过20dB。由此可见跨分割布线会造成很大的电磁干扰,不仅干扰自身,同时它的电磁辐射还会对周围其他的电路或系统造成干扰。因此,我们在布线的时候一定要注意,尽量避免跨分割走线。

三、PCB板避免跨分割的办法

跨分割走线给电路带来很大的危害,我们在实际电路的时候,应该尽量避免造成跨分割现象,主要注意以下几点:

(1)走线避免穿越分割带,走线的时候考虑地、电源的分割,让走线绕开电源的分割问题,

也可以增加电路的叠层数来避免跨分割问题。

(2)通常布线的时候,电源分割是在不信号线之后设计,做电源或地分割时,一定要注意在地、电源分割的时候,会对哪些信号造成影响,会造成哪些信号线的跨分割走线,哪些是我们可以避免的,注意适当地调整地、电源分割。

(3)过孔设计和散孔不应过于密集,造成地、电源平面的隔离带。

(4)插装器件或者接插件在定义时,要分布地合理,充分考虑对地、电源平面的影响,是否造成分割,导致EMI增强。

一、PCB板的跨分割设计

电路上PCB走线穿过地(电源)层分割,信号的完整性会受到很大的影响,以及电路的EMI和EMC特性也发生变化,这就是跨分割问题。这些也往往是电子工程师容易忽略的问题。跨分割问题的产生主要有两个来源:

1、电源/地平面的分割

如图4-12所示,在同一层(地层)上有模拟地和数字地的分割。当PCB走线穿过这个分割带时,跨分割问题产生了。

2、密集过孔或密集插装(压接)器件管脚定义不当造成的分割

密集过孔或密集插装(压接)器件在管脚定义时如果分布得不合理,而管脚之间的距离很小,会在地层或者定义层造成了一个狭长的隔离带。如果有走线穿过这个分割,就造成做跨分割现象。

我们先看看如图4-13所示的走线。

这些布线表面上无可挑剔:整齐,漂亮,也是一般电子或电路工程师所喜欢的布线方式。我们再看一下这些过孔对应区域的电源/地平面(图6-14),就会发现产生了电源、地层分割问题。

在图4-13 中,由于过孔间距过近,在电源/地平面上造成一条长长分割带,如图4-14所示,如果有走线穿过这个分割带时,跨分割问题也产生了。这类问题主要出现在电路中总线布线时容易出现,必须引起广大工程师的注意。

同样地,当通孔(包括焊盘和过孔)穿过地/电源平面时,如果通孔之间的距离靠得过近,上述问题也就同样出现了。这类问题主要出现在密集插装(压接)器件管脚定义不当时容易出现。因此,在定义密集插装(压接)器件管脚信号时,不仅要考虑信号的个数种类,还必须考虑信号总线的排列方式,避免对电源、地平面造成分割带来跨分割问题。

二、PCB板的跨分割走线的危害

跨分割走线的主要危害包括:

(1)导致走线的阻抗不连续;

(2)容易使信号之间发生串扰;

(3)可能引起信号的反射;

(4)增大电流环路面积,加大环路电感,使输出的波形容易振荡;

(5)增加向空间的辐射干扰,同时易受空间磁场的影响;

(6)加大与板上其他电路产生磁场耦合的可能性;

(7)环路电感上的高频压降构成共模辐射源,并通过外接电缆产生共模辐射。

为了形象地描述跨分割走线对电路的危害,我们用图4-15给出了一个地槽引起高频信号产生串扰的示意图。

对于需要严格的阻抗控制、按带状线模型走线的高速信号线而言,还会因为上平面、下平面或上下平面的开槽破坏带状线模型,造成阻抗的不连续,引起严重的信号失真,使信号的可靠度下降。

为了形象地描述跨分割走线对电磁干扰的影响,笔者进行“了试验对比。从对比的结果很容易看到跨分割的影响。

在一块PCB板上布了两根走线,两者激励源相同,负载完全一样,均走在同一布线层,长度均为6000MIL,惟一不同的是,一个跨了平面分割,另外一个参考平面完整。通过开关切换,在保证外部条件完全相同的情况下,分别让其中的一个网络上电,在半波暗室测试结果如下:

从图4-16和图4-17可以清楚地看出:信号跨分割区会增加辐射8dB-10dB;具体增加的辐射强度取决于跨分割导致的回流路径回路面积的大小,也与周围的电磁干扰环境有关。如果一条时钟线在对外接口线缆附近跨分割布线,其导致的电磁干扰强度可能超过20dB。由此可见跨分割布线会造成很大的电磁干扰,不仅干扰自身,同时它的电磁辐射还会对周围其他的电路或系统造成干扰。因此,我们在布线的时候一定要注意,尽量避免跨分割走线。

三、PCB板避免跨分割的办法

跨分割走线给电路带来很大的危害,我们在实际电路的时候,应该尽量避免造成跨分割现象,主要注意以下几点:

(1)走线避免穿越分割带,走线的时候考虑地、电源的分割,让走线绕开电源的分割问题,

也可以增加电路的叠层数来避免跨分割问题。

(2)通常布线的时候,电源分割是在不信号线之后设计,做电源或地分割时,一定要注意在地、电源分割的时候,会对哪些信号造成影响,会造成哪些信号线的跨分割走线,哪些是我们可以避免的,注意适当地调整地、电源分割。

(3)过孔设计和散孔不应过于密集,造成地、电源平面的隔离带。

(4)插装器件或者接插件在定义时,要分布地合理,充分考虑对地、电源平面的影响,是否造成分割,导致EMI增强。

1、3点以上连线,尽量让线依次通过各点,便于测试,线长尽量短,如下图(按前一种):

2、引脚之间尽量不要放线,特别是集成电路引脚之间和周围。

3、不同层之间的线尽量不要平行,以免形成实际上的电容。

4、布线尽量是直线,或45度折线,避免产生电磁辐射。

5、地线、电源线至少10-15mil以上(对逻辑电路)。

6、尽量让铺地多义线连在一起,增大接地面积。线与线之间尽量整齐。

7、注意元件排放均匀,以便安装、插件、焊接操作。文字排放在当前字符层,位置合理,注意朝向,避免被遮挡,便于生产。

8、元件排放多考虑结构,贴片元件有正负极应在封装和最后标明,避免空间冲突。

9、目前印制板可作4—5mil的布线,但通常作6mil线宽,8mil线距,12/20mil焊盘。布线应考虑灌入电流等的影响。

10、功能块元件尽量放在一起,斑马条等LCD附近元件不能靠之太近。

11、过孔要涂绿油(置为负一倍值)。

12、电池座下最好不要放置焊盘、过空等,PAD和VIL尺寸合理。

13、布线完成后要仔细检查每一个联线(包括NETLABLE)是否真的连接上(可用点亮法)。

14、振荡电路元件尽量靠近IC,振荡电路尽量远离天线等易受干扰区。晶振下要放接地焊盘。

15、多考虑加固、挖空放元件等多种方式,避免辐射源过多。

16、设计流程:

A:设计原理图;

B:确认原理;

C:检查电器连接是否完全;

D:检查是否封装所有元件,是否尺寸正确;

E:放置元件;

F:检查元件位置是否合理(可打印1:1图比较);

G:可先布地线和电源线;

H:检查有无飞线(可关掉除飞线层外其他层);

I:优化布线;

J:再检查布线完整性;

K:比较网络表,查有无遗漏;

L:规则校验,有无不应该的错误标号;

M:文字说明整理;

N:添加制板标志性文字说明;

O:综合性检查。

2、引脚之间尽量不要放线,特别是集成电路引脚之间和周围。

3、不同层之间的线尽量不要平行,以免形成实际上的电容。

4、布线尽量是直线,或45度折线,避免产生电磁辐射。

5、地线、电源线至少10-15mil以上(对逻辑电路)。

6、尽量让铺地多义线连在一起,增大接地面积。线与线之间尽量整齐。

7、注意元件排放均匀,以便安装、插件、焊接操作。文字排放在当前字符层,位置合理,注意朝向,避免被遮挡,便于生产。

8、元件排放多考虑结构,贴片元件有正负极应在封装和最后标明,避免空间冲突。

9、目前印制板可作4—5mil的布线,但通常作6mil线宽,8mil线距,12/20mil焊盘。布线应考虑灌入电流等的影响。

10、功能块元件尽量放在一起,斑马条等LCD附近元件不能靠之太近。

11、过孔要涂绿油(置为负一倍值)。

12、电池座下最好不要放置焊盘、过空等,PAD和VIL尺寸合理。

13、布线完成后要仔细检查每一个联线(包括NETLABLE)是否真的连接上(可用点亮法)。

14、振荡电路元件尽量靠近IC,振荡电路尽量远离天线等易受干扰区。晶振下要放接地焊盘。

15、多考虑加固、挖空放元件等多种方式,避免辐射源过多。

16、设计流程:

A:设计原理图;

B:确认原理;

C:检查电器连接是否完全;

D:检查是否封装所有元件,是否尺寸正确;

E:放置元件;

F:检查元件位置是否合理(可打印1:1图比较);

G:可先布地线和电源线;

H:检查有无飞线(可关掉除飞线层外其他层);

I:优化布线;

J:再检查布线完整性;

K:比较网络表,查有无遗漏;

L:规则校验,有无不应该的错误标号;

M:文字说明整理;

N:添加制板标志性文字说明;

O:综合性检查。