相同容值电容的并联

使用很多电容并联能有效地减小阻抗。63个0.0316 uF的小电容(每个电容ESL为1 nH)并联的效果相当于一个具有0.159 nH ESL的1.9908 uF电容。

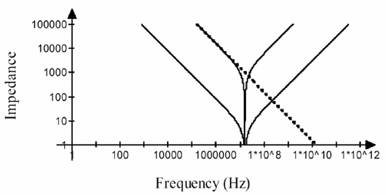

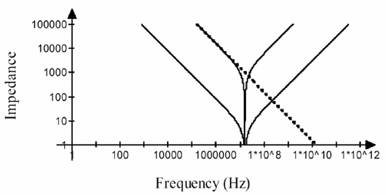

图10 多个等值电容并联

单个电容及并联电容的阻抗特性如图10所示。并联后仍有相同的谐振频率,但是并联电容在每一个频率点上的阻抗都小于单个电容。

但是,从图中我们看到,阻抗曲线呈V字型,随着频率偏离谐振点,其阻抗仍然上升的很快。要在很宽的频率范围内满足目标阻抗要求,需要并联大量的同值电容。这不是一种好的方法,造成极大地浪费。有些人喜欢在电路板上放置很多0.1uF电容,如果你设计的电路工作频率很高,信号变化很快,那就不要这样做,最好使用不同容值的组合来构成相对平坦的阻抗曲线。

使用很多电容并联能有效地减小阻抗。63个0.0316 uF的小电容(每个电容ESL为1 nH)并联的效果相当于一个具有0.159 nH ESL的1.9908 uF电容。

图10 多个等值电容并联

单个电容及并联电容的阻抗特性如图10所示。并联后仍有相同的谐振频率,但是并联电容在每一个频率点上的阻抗都小于单个电容。

但是,从图中我们看到,阻抗曲线呈V字型,随着频率偏离谐振点,其阻抗仍然上升的很快。要在很宽的频率范围内满足目标阻抗要求,需要并联大量的同值电容。这不是一种好的方法,造成极大地浪费。有些人喜欢在电路板上放置很多0.1uF电容,如果你设计的电路工作频率很高,信号变化很快,那就不要这样做,最好使用不同容值的组合来构成相对平坦的阻抗曲线。

有两种方法确定所需的电容量。第一种方法利用电源驱动的负载计算电容量。这种方法没有考虑ESL及ESR的影响,因此很不精确,但是对理解电容量的选择有好处。第二种方法就是利用目标阻抗(Target Impedance)来计算总电容量,这是业界通用的方法,得到了广泛验证。你可以先用这种方法来计算,然后做局部微调,能达到很好的效果,如何进行局部微调,是一个更高级的话题。下面分别介绍两种方法。

方法一:利用电源驱动的负载计算电容量

设负载(容性)为30pF,要在2ns内从0V驱动到3.3V,瞬态电流为:

(公式5)

如果共有36个这样的负载需要驱动,则瞬态电流为:36*49.5mA=1.782A。假设容许电压波动为:3.3*2.5%=82.5 mV,所需电容量为

C=I*dt/dv=1.782A*2ns/0.0825V=43.2nF

说明:所加的电容实际上作为抑制电压波纹的储能元件,该电容必须在2ns内为负载提供1.782A的电流,同时电压下降不能超过82.5 mV,因此电容值应根据82.5 mV来计算。记住:电容放电给负载提供电流,其本身电压也会下降,但是电压下降的量不能超过82.5 mV(容许的电压波纹)。这种计算没什么实际意义,之所以放在这里说一下,是为了让大家对去耦原理认识更深。

方法二:利用目标阻抗计算电容量(设计思想很严谨,要吃透)

为了清楚的说明电容量的计算方法,我们用一个例子。要去耦的电源为1.2V,容许电压波动为2.5%,最大瞬态电流600mA,

第一步:计算目标阻抗

第二步:确定稳压电源频率响应范围。

和具体使用的电源片子有关,通常在DC到几百kHz之间。这里设为DC到100kHz。在100kHz以下时,电源芯片能很好的对瞬态电流做出反应,高于100kHz时,表现为很高的阻抗,如果没有外加电容,电源波动将超过允许的2.5%。为了在高于100kHz时仍满足电压波动小于2.5%要求,应该加多大的电容?

第三步:计算bulk电容量

当频率处于电容自谐振点以下时,电容的阻抗可近似表示为:

频率f越高,阻抗越小,频率越低,阻抗越大。在感兴趣的频率范围内,电容的最大阻抗不能超过目标阻抗,因此使用100kHz计算(电容起作用的频率范围的最低频率,对应电容最高阻抗)。

第四步:计算bulk电容的最高有效频率

当频率处于电容自谐振点以上时,电容的阻抗可近似表示为:

频率f越高,阻抗越大,但阻抗不能超过目标阻抗。假设ESL为5nH,则最高有效频率为: 。这样一个大的电容能够让我们把电源阻抗在100kHz到1.6MHz之间控制在目标阻抗之下。当频率高于1.6MHz时,还需要额外的电容来控制电源系统阻抗。

。这样一个大的电容能够让我们把电源阻抗在100kHz到1.6MHz之间控制在目标阻抗之下。当频率高于1.6MHz时,还需要额外的电容来控制电源系统阻抗。

第五步:计算频率高于1.6MHz时所需电容

如果希望电源系统在500MHz以下时都能满足电压波动要求,就必须控制电容的寄生电感量。必须满足 ,所以有:

,所以有:

假设使用AVX公司的0402封装陶瓷电容,寄生电感约为0.4nH,加上安装到电路板上后过孔的寄生电感(本文后面有计算方法)假设为0.6nH,则总的寄生电感为1 nH。为了满足总电感不大于0.16 nH的要求,我们需要并联的电容个数为:1/0.016=62.5个,因此需要63个0402电容。

为了在1.6MHz时阻抗小于目标阻抗,需要电容量为:

因此每个电容的电容量为1.9894/63=0.0316 uF。

综上所述,对于这个系统,我们选择1个31.831 uF的大电容和63个0.0316 uF的小电容即可满足要求。

注意:以上基于目标阻抗(Target Impedance)的计算,只是为了说明这种方法的基本原理,实际中不能这样简单的计算就了事,因为还有很多问题需要考虑。学习的重点是这种方法的核心思想。

方法一:利用电源驱动的负载计算电容量

设负载(容性)为30pF,要在2ns内从0V驱动到3.3V,瞬态电流为:

(公式5)

如果共有36个这样的负载需要驱动,则瞬态电流为:36*49.5mA=1.782A。假设容许电压波动为:3.3*2.5%=82.5 mV,所需电容量为

C=I*dt/dv=1.782A*2ns/0.0825V=43.2nF

说明:所加的电容实际上作为抑制电压波纹的储能元件,该电容必须在2ns内为负载提供1.782A的电流,同时电压下降不能超过82.5 mV,因此电容值应根据82.5 mV来计算。记住:电容放电给负载提供电流,其本身电压也会下降,但是电压下降的量不能超过82.5 mV(容许的电压波纹)。这种计算没什么实际意义,之所以放在这里说一下,是为了让大家对去耦原理认识更深。

方法二:利用目标阻抗计算电容量(设计思想很严谨,要吃透)

为了清楚的说明电容量的计算方法,我们用一个例子。要去耦的电源为1.2V,容许电压波动为2.5%,最大瞬态电流600mA,

第一步:计算目标阻抗

第二步:确定稳压电源频率响应范围。

和具体使用的电源片子有关,通常在DC到几百kHz之间。这里设为DC到100kHz。在100kHz以下时,电源芯片能很好的对瞬态电流做出反应,高于100kHz时,表现为很高的阻抗,如果没有外加电容,电源波动将超过允许的2.5%。为了在高于100kHz时仍满足电压波动小于2.5%要求,应该加多大的电容?

第三步:计算bulk电容量

当频率处于电容自谐振点以下时,电容的阻抗可近似表示为:

频率f越高,阻抗越小,频率越低,阻抗越大。在感兴趣的频率范围内,电容的最大阻抗不能超过目标阻抗,因此使用100kHz计算(电容起作用的频率范围的最低频率,对应电容最高阻抗)。

第四步:计算bulk电容的最高有效频率

当频率处于电容自谐振点以上时,电容的阻抗可近似表示为:

频率f越高,阻抗越大,但阻抗不能超过目标阻抗。假设ESL为5nH,则最高有效频率为:

。这样一个大的电容能够让我们把电源阻抗在100kHz到1.6MHz之间控制在目标阻抗之下。当频率高于1.6MHz时,还需要额外的电容来控制电源系统阻抗。

。这样一个大的电容能够让我们把电源阻抗在100kHz到1.6MHz之间控制在目标阻抗之下。当频率高于1.6MHz时,还需要额外的电容来控制电源系统阻抗。第五步:计算频率高于1.6MHz时所需电容

如果希望电源系统在500MHz以下时都能满足电压波动要求,就必须控制电容的寄生电感量。必须满足

,所以有:

,所以有:

假设使用AVX公司的0402封装陶瓷电容,寄生电感约为0.4nH,加上安装到电路板上后过孔的寄生电感(本文后面有计算方法)假设为0.6nH,则总的寄生电感为1 nH。为了满足总电感不大于0.16 nH的要求,我们需要并联的电容个数为:1/0.016=62.5个,因此需要63个0402电容。

为了在1.6MHz时阻抗小于目标阻抗,需要电容量为:

因此每个电容的电容量为1.9894/63=0.0316 uF。

综上所述,对于这个系统,我们选择1个31.831 uF的大电容和63个0.0316 uF的小电容即可满足要求。

注意:以上基于目标阻抗(Target Impedance)的计算,只是为了说明这种方法的基本原理,实际中不能这样简单的计算就了事,因为还有很多问题需要考虑。学习的重点是这种方法的核心思想。

著名的Target Impedance(目标阻抗)

目标阻抗(Target Impedance)定义为:

(公式4)

其中: 为要进行去耦的电源电压等级,常见的有5V、3.3V、1.8V、1.26V、1.2V等。 为允许的电压波动,在电源噪声余量一节中我们已经阐述过了,典型值为2.5%。 为负载芯片的最大瞬态电流变化量。

该定义可解释为:能满足负载最大瞬态电流供应,且电压变化不超过最大容许波动范围的情况下,电源系统自身阻抗的最大值。超过这一阻抗值,电源波动将超过容许范围。如果你对阻抗和电压波动的关系不清楚的话,请回顾“电容退耦的两种解释”一节。

对目标阻抗有两点需要说明:

1 目标阻抗是电源系统的瞬态阻抗,是对快速变化的电流表现出来的一种阻抗特性。

2 目标阻抗和一定宽度的频段有关。在感兴趣的整个频率范围内,电源阻抗都不能超过这个值。阻抗是电阻、电感和电容共同作用的结果,因此必然与频率有关。感兴趣的整个频率范围有多大?这和负载对瞬态电流的要求有关。顾名思义,瞬态电流是指在极短时间内电源必须提供的电流。如果把这个电流看做信号的话,相当于一个阶跃信号,具有很宽的频谱,这一频谱范围就是我们感兴趣的频率范围。

如果暂时不理解上述两点,没关系,继续看完本文后面的部分,你就明白了。

目标阻抗(Target Impedance)定义为:

(公式4)

其中: 为要进行去耦的电源电压等级,常见的有5V、3.3V、1.8V、1.26V、1.2V等。 为允许的电压波动,在电源噪声余量一节中我们已经阐述过了,典型值为2.5%。 为负载芯片的最大瞬态电流变化量。

该定义可解释为:能满足负载最大瞬态电流供应,且电压变化不超过最大容许波动范围的情况下,电源系统自身阻抗的最大值。超过这一阻抗值,电源波动将超过容许范围。如果你对阻抗和电压波动的关系不清楚的话,请回顾“电容退耦的两种解释”一节。

对目标阻抗有两点需要说明:

1 目标阻抗是电源系统的瞬态阻抗,是对快速变化的电流表现出来的一种阻抗特性。

2 目标阻抗和一定宽度的频段有关。在感兴趣的整个频率范围内,电源阻抗都不能超过这个值。阻抗是电阻、电感和电容共同作用的结果,因此必然与频率有关。感兴趣的整个频率范围有多大?这和负载对瞬态电流的要求有关。顾名思义,瞬态电流是指在极短时间内电源必须提供的电流。如果把这个电流看做信号的话,相当于一个阶跃信号,具有很宽的频谱,这一频谱范围就是我们感兴趣的频率范围。

如果暂时不理解上述两点,没关系,继续看完本文后面的部分,你就明白了。

从电源系统的角度进行去耦设计

先插一句题外话,很多人在看资料时会有这样的困惑,有的资料上说要对每个电源引脚加去耦电容,而另一些资料并不是按照每个电源引脚都加去偶电容来设计的,只是说在芯片周围放置多少电容,然后怎么放置,怎么打孔等等。那么到底哪种说法及做法正确呢?我在刚接触电路设计的时候也有这样的困惑。其实,两种方法都是正确的,只不过处理问题的角度不同。看过本文后,你就彻底明白了。

上一节讲了对引脚去耦的方法,这一节就来讲讲另一种方法,从电源系统的角度进行去耦设计。该方法本着这样一个原则:在感兴趣的频率范围内,使整个电源分配系统阻抗最低。其方法仍然是使用去耦电容。

电源去耦涉及到很多问题:总的电容量多大才能满足要求?如何确定这个值?选择那些电容值?放多少个电容?选什么材质的电容?电容如何安装到电路板上?电容放置距离有什么要求?下面分别介绍。

先插一句题外话,很多人在看资料时会有这样的困惑,有的资料上说要对每个电源引脚加去耦电容,而另一些资料并不是按照每个电源引脚都加去偶电容来设计的,只是说在芯片周围放置多少电容,然后怎么放置,怎么打孔等等。那么到底哪种说法及做法正确呢?我在刚接触电路设计的时候也有这样的困惑。其实,两种方法都是正确的,只不过处理问题的角度不同。看过本文后,你就彻底明白了。

上一节讲了对引脚去耦的方法,这一节就来讲讲另一种方法,从电源系统的角度进行去耦设计。该方法本着这样一个原则:在感兴趣的频率范围内,使整个电源分配系统阻抗最低。其方法仍然是使用去耦电容。

电源去耦涉及到很多问题:总的电容量多大才能满足要求?如何确定这个值?选择那些电容值?放多少个电容?选什么材质的电容?电容如何安装到电路板上?电容放置距离有什么要求?下面分别介绍。

局部去耦设计方法

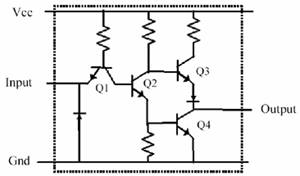

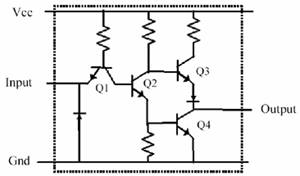

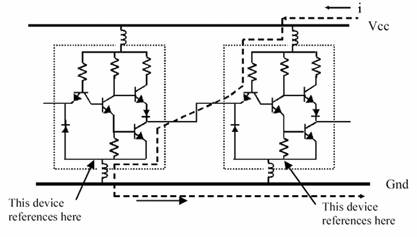

我们从一个典型逻辑电路入手,讨论局部退耦设计方法。图7是典型的非门(NOT GATE)电路。当输入(Input)低电平时,Q1打开,拉低Q2的基极,因此Q4的基极被拉低,Q3打开,输出(Output)高电平。

图7 非门内部逻辑

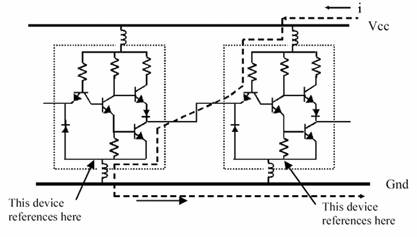

实际电路设计中,器件之间相互连接构成完整系统,因此器件之间必然存在相互影响。作为例子,我们级联两个非门,如图8所示,看看两个器件之间怎样相互影响。理想的情况应该是:第一个非门输入逻辑低电平(逻辑0),其输出为高电平,第二个非门输入为第一个的输出,也为高电平,因此第二个非门输出低电平。

为保证逻辑电路能正常工作,表征电路逻辑状态的电平值必须落在一定范围内。比如对于3.3V逻辑,高电平大于2V为逻辑1,低电平小于0.8V为逻辑0。当逻辑门电路的输入电平处于上述范围内时,电路能保证对输入逻辑状态的正确判断。当电平值处于0.8V到2V之间时,则不能保证对输入逻辑状态的正确判断,对于本例的非门来说,其输出可能是逻辑0,也可能是逻辑1,或者处于不定态。因此输入电平超出规定范围时,可能发生逻辑错误。

逻辑电路在设计时采用了很多技术来保证器件本身不会发生这样的错误。但是,当器件安装到电路板上,板级系统的其他因素仍可能导致类似错误的发生。图8中级联的两个非门共用电源端Vcc和接地端GND。Vcc到每个非门供电引脚间都会存在寄生电感,每个非门的地引脚到GND之间也同样存在寄生电感。在实际板级电路中设计中,寄生电感不可避免,电源平面、地平面、过孔、焊盘、连接焊盘的引出线都会引入额外的寄生电感。图8已经画出了电源端和地端的寄生电感。当第一个非门输入高电平,其输出低电平。此时将会形成图中虚线所示的电流通路,第一个非门接地处寄生电感上的电压为:V=L*di/dt。这里i为逻辑转换过程形成的瞬态电流。如果电路转换过程非常快(高速器件内部晶体管转换时间已经降到了皮秒级),di/dt将是个很大的值,即使很小的寄生电感L也会在电感两端感应出很大的电压V。对于一些大规模逻辑芯片,接地引脚是内部非常多的晶体管共用的,这些晶体管同时开关的话,将产生很大的瞬态电流,再加上极快的转换时间,寄生电感上的感应电压更大。此时第一个非门的输出信号电平为:非门本身低电平电压+寄生电感上的电压。如果这一值接近2V,可能会被第二个非门判断为逻辑1,从而发生逻辑错误。

图8 级联的非门

寄生电感可能引起电路逻辑错误,那么如何解决这一问题?

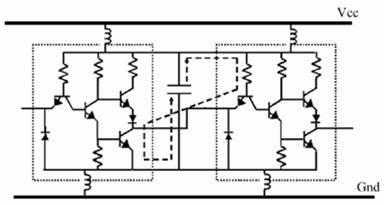

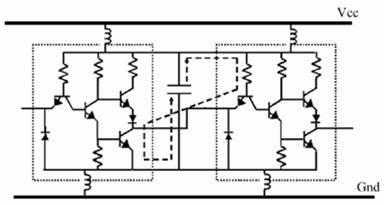

图9展示了一种解决方法。把电容紧邻器件放置,跨接在电源引脚和地引脚之间。正常时,电容充电,存储一部分电荷。当非门发生翻转瞬间,电容放电,形成瞬间的浪涌电流,方向如图9中虚线所示。这样电路转换所需的瞬态电流不必再由VCC提供,电容相当于局部小电源。因此电源端和地端的寄生电感被旁路掉了,寄生电感在这一瞬间没有电流流过,因而也不存在感应电压,这就保证了第一个非门输出信号的逻辑电平值的正确性。

图9 局部去耦

所需电容可能不是一个,通常是两个或多个电容并联放置,减小电容本身的串联电感,进而减小电容充放电回路的阻抗。电容的摆放、安装距离、安装方法、电容选择等问题,本文后面会详细介绍。

很多芯片制造商在参考设计中给出的都是这种局部去耦方式,但并不是说这种方式就是最优的。芯片商关心的是如何提高他所提供的特定器件的性能,也就是说,着眼点在器件本身,并没有从整个电路系统的角度来处理电源去耦的问题。有时你会发现,对每一个的电源和地引脚都单独去耦是不现实的,可能是空间限制,放不下如此多的电容,也可能是成本限制。因此对于板级集成的工程师来说,除了要熟悉局部去耦的方法外,还要深入研究如何从整个电源分配系统的角度进行电源去耦设计。

我们从一个典型逻辑电路入手,讨论局部退耦设计方法。图7是典型的非门(NOT GATE)电路。当输入(Input)低电平时,Q1打开,拉低Q2的基极,因此Q4的基极被拉低,Q3打开,输出(Output)高电平。

图7 非门内部逻辑

实际电路设计中,器件之间相互连接构成完整系统,因此器件之间必然存在相互影响。作为例子,我们级联两个非门,如图8所示,看看两个器件之间怎样相互影响。理想的情况应该是:第一个非门输入逻辑低电平(逻辑0),其输出为高电平,第二个非门输入为第一个的输出,也为高电平,因此第二个非门输出低电平。

为保证逻辑电路能正常工作,表征电路逻辑状态的电平值必须落在一定范围内。比如对于3.3V逻辑,高电平大于2V为逻辑1,低电平小于0.8V为逻辑0。当逻辑门电路的输入电平处于上述范围内时,电路能保证对输入逻辑状态的正确判断。当电平值处于0.8V到2V之间时,则不能保证对输入逻辑状态的正确判断,对于本例的非门来说,其输出可能是逻辑0,也可能是逻辑1,或者处于不定态。因此输入电平超出规定范围时,可能发生逻辑错误。

逻辑电路在设计时采用了很多技术来保证器件本身不会发生这样的错误。但是,当器件安装到电路板上,板级系统的其他因素仍可能导致类似错误的发生。图8中级联的两个非门共用电源端Vcc和接地端GND。Vcc到每个非门供电引脚间都会存在寄生电感,每个非门的地引脚到GND之间也同样存在寄生电感。在实际板级电路中设计中,寄生电感不可避免,电源平面、地平面、过孔、焊盘、连接焊盘的引出线都会引入额外的寄生电感。图8已经画出了电源端和地端的寄生电感。当第一个非门输入高电平,其输出低电平。此时将会形成图中虚线所示的电流通路,第一个非门接地处寄生电感上的电压为:V=L*di/dt。这里i为逻辑转换过程形成的瞬态电流。如果电路转换过程非常快(高速器件内部晶体管转换时间已经降到了皮秒级),di/dt将是个很大的值,即使很小的寄生电感L也会在电感两端感应出很大的电压V。对于一些大规模逻辑芯片,接地引脚是内部非常多的晶体管共用的,这些晶体管同时开关的话,将产生很大的瞬态电流,再加上极快的转换时间,寄生电感上的感应电压更大。此时第一个非门的输出信号电平为:非门本身低电平电压+寄生电感上的电压。如果这一值接近2V,可能会被第二个非门判断为逻辑1,从而发生逻辑错误。

图8 级联的非门

寄生电感可能引起电路逻辑错误,那么如何解决这一问题?

图9展示了一种解决方法。把电容紧邻器件放置,跨接在电源引脚和地引脚之间。正常时,电容充电,存储一部分电荷。当非门发生翻转瞬间,电容放电,形成瞬间的浪涌电流,方向如图9中虚线所示。这样电路转换所需的瞬态电流不必再由VCC提供,电容相当于局部小电源。因此电源端和地端的寄生电感被旁路掉了,寄生电感在这一瞬间没有电流流过,因而也不存在感应电压,这就保证了第一个非门输出信号的逻辑电平值的正确性。

图9 局部去耦

所需电容可能不是一个,通常是两个或多个电容并联放置,减小电容本身的串联电感,进而减小电容充放电回路的阻抗。电容的摆放、安装距离、安装方法、电容选择等问题,本文后面会详细介绍。

很多芯片制造商在参考设计中给出的都是这种局部去耦方式,但并不是说这种方式就是最优的。芯片商关心的是如何提高他所提供的特定器件的性能,也就是说,着眼点在器件本身,并没有从整个电路系统的角度来处理电源去耦的问题。有时你会发现,对每一个的电源和地引脚都单独去耦是不现实的,可能是空间限制,放不下如此多的电容,也可能是成本限制。因此对于板级集成的工程师来说,除了要熟悉局部去耦的方法外,还要深入研究如何从整个电源分配系统的角度进行电源去耦设计。